Science Score: 44.0%

This score indicates how likely this project is to be science-related based on various indicators:

-

✓CITATION.cff file

Found CITATION.cff file -

✓codemeta.json file

Found codemeta.json file -

✓.zenodo.json file

Found .zenodo.json file -

○DOI references

-

○Academic publication links

-

○Academic email domains

-

○Institutional organization owner

-

○JOSS paper metadata

-

○Scientific vocabulary similarity

Low similarity (7.9%) to scientific vocabulary

Keywords

Repository

UART implementation in VHDL

Basic Info

Statistics

- Stars: 1

- Watchers: 2

- Forks: 0

- Open Issues: 0

- Releases: 1

Topics

Metadata Files

README.md

uart-vhdl

UART implementation in VHDL

UART_RX Module

Generic and Port Description

| Generic Name | Data Type | Comment | ------ | ------ | ------ | | CLKFREQ | integer | Set system clock frequency in Hz (Default: 100 MHz) | BAUDRATE | integer | Baudrate value | PARITY_BIT| string | valid for "none" only!

| Port Name | Data Type | Direction | Comment | ------ | ------ | ------ | ----- | | iclk | stdlogic | input | clock | irst | stdlogic | input | reset (active high) | irx| stdlogic | input | uart rx pin | odata| stdlogic | output | received data | ovalid| stdlogic | output | '1' when data received else '0' | obusy| stdlogic | output | '1' during the receiving process else '0'

UART_TX Module

Generic and Port Description

| Generic Name | Data Type | Comment | ------ | ------ | ------ | | CLKFREQ | integer | Set system clock frequency in Hz (Default: 100 MHz) | BAUDRATE | integer | Baudrate value | PARITY_BIT| string | valid for "none" only!

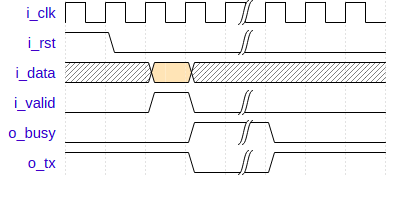

| Port Name | Data Type | Direction | Comment | ------ | ------ | ------ | ----- | | iclk | stdlogic | input | clock | irst | stdlogic | input | reset (active high) | idata| stdlogic | input | data to be sent | ivalid| stdlogic | input | set '1' if idata is valid else '0' | otx| stdlogic | output | uart tx pin | obusy| std_logic | output | '1' during the transmission process else '0'

Timing Diagram

Warning!:

You cannot send multiple data one after another. You can use the condition below on your code.if(uart_tx_busy = '0' and uart_tx_valid = '0') then uart_tx_data <= <YOUR DATA>; uart_tx_valid <= '1'; else uart_tx_valid <= '0'; end if;Directory Tree

├── src │ ├── uart_rx_comp.vhd -- UART rx component package. You can check sim/tb/uart_tb.vhd for usage. │ ├── uart_rx.vhd -- UART rx module. │ ├── uart_tx_comp.vhd -- UART tx component package. You can check sim/tb/uart_tb.vhd for usage. │ └── uart_tx.vhd -- UART tx module. └── sim └── uart_tb.vhd -- Example usage for both tx and rx modules. (Testbench) ├── scripts ├── run_sim.tcl -- Simulation script for simulation. ├── compile_src.tcl -- Simulation script for simulation. └── compile_sim.vhd -- Example usage for both tx and rx modules. (Testbench)

This project is under development!

Owner

- Name: Koç University - Magnonic and Photonic Devices Research Group

- Login: onbasligroup

- Kind: organization

- Repositories: 1

- Profile: https://github.com/onbasligroup

Citation (CITATION.cff)

cff-version: 1.2.0 message: "If you use this software, please cite it as below." authors: - family-names: "Tufan" given-names: "Buğra" orcid: "https://orcid.org/0000-0002-4777-9854" title: "UART Implementation in VHDL" version: 1.0 date-released: 2022-11-22 url: "https://github.com/onbasligroup/uart-vhdl"

GitHub Events

Total

- Watch event: 1

Last Year

- Watch event: 1